# NRC Publications Archive Archives des publications du CNRC

Instructions for sweep delay unit no. 74A (A.A.No.4 Mk.6/1)

National Research Council of Canada. Radio and Electrical Engineering

Division

For the publisher's version, please access the DOI link below./ Pour consulter la version de l'éditeur, utilisez le lien DOI ci-dessous.

#### Publisher's version / Version de l'éditeur:

https://doi.org/10.4224/21273084

Report (National Research Council of Canada. Radio and Electrical Engineering Division: ERB); no. ERB-273, 1951-11

NRC Publications Archive Record / Notice des Archives des publications du CNRC : <a href="https://nrc-publications.canada.ca/eng/view/object/?id=188985d6-5255-4778-8f12-c30e523253b0">https://nrc-publications.canada.ca/eng/view/object/?id=188985d6-5255-4778-8f12-c30e523253b0</a> https://publications-cnrc.canada.ca/fra/voir/objet/?id=188985d6-5255-4778-8f12-c30e523253b0

Access and use of this website and the material on it are subject to the Terms and Conditions set forth at <a href="https://nrc-publications.canada.ca/eng/copyright">https://nrc-publications.canada.ca/eng/copyright</a>

READ THESE TERMS AND CONDITIONS CAREFULLY BEFORE USING THIS WEBSITE.

L'accès à ce site Web et l'utilisation de son contenu sont assujettis aux conditions présentées dans le site <a href="https://publications-cnrc.canada.ca/fra/droits">https://publications-cnrc.canada.ca/fra/droits</a>

LISEZ CES CONDITIONS ATTENTIVEMENT AVANT D'UTILISER CE SITE WEB.

Questions? Contact the NRC Publications Archive team at

PublicationsArchive-ArchivesPublications@nrc-cnrc.gc.ca. If you wish to email the authors directly, please see the first page of the publication for their contact information.

**Vous avez des questions?** Nous pouvons vous aider. Pour communiquer directement avec un auteur, consultez la première page de la revue dans laquelle son article a été publié afin de trouver ses coordonnées. Si vous n'arrivez pas à les repérer, communiquez avec nous à PublicationsArchive-ArchivesPublications@nrc-cnrc.gc.ca.

ERB - 273

## RESTRETED

NATIONAL RESEARCH COUNCIL OF CANADA RADIO AND ELECTRICAL ENGINEERING DIVISION

CANADA INSTITUTE FOR S.T.I. N.R C.C.

ANALYZED

MAY 1 6 1995

INSTITUT CANADIEN DE L'I.S.T.

C.N. R.C.

INSTRUCTIONS FOR SWEEP DELAY UNIT NO. 74A (A.A. NO. 4 MK. 6/1)

OTTAWA

NOVEMBER 1951

INSTRUCTIONS FOR SWEEF DELAY UNIT No. Tha (A.A.No.h MR. 6/1)

#### GENERAL DESCRIPTION

The maximum range that can be displayed with the present sweep is 120,000 yards. By the addition of Sweep Delay Unit No.744 the maximum displayable range may be increased by approximately 80,000 to 100,000 yards. This is accomplished by delaying the initiation of the sweep fer a predetermined time interval after the transmitter pulse. This delay can be calibrated by reference to the calibration rings on the PPI. Unit No.744 may be switched in or out of the circuit, as dealers.

INSTRUCTIONS FOR SWEEP DELAY UNIT No.74A (A.A.No.4 Mk.6/1)

DETAILED TECHNICAL DESCRIPTION

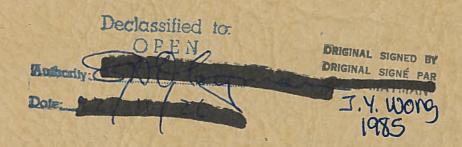

#### ACTION OF DELAY CHASSIS SWITCH (see Figs. 1 and 2)

- NORMAL chassis to give normal instantaneous sweep triggering with the B+ for the blocking "escillator" switched off.

- Position (2) The input trigger from the modulator is delayed by using it to trigger a phantastron. The trailing edge of its output triggers a blooking pulse generator whose output pulse starts the samep on the PPI.

- CAL.

CAL.

#### INSTRUCTIONS FOR SWEEP DELAY UNIT No.74A (A.A.No.4 Mk.6/1)

I

#### GENERAL DESCRIPTION

The maximum range that can be displayed with the present sweep is 120,000 yards. By the addition of Sweep Delay Unit No.74A the maximum displayable range may be increased by approximately 40,000 to 100,000 yards. This is accomplished by delaying the initiation of the sweep for a predetermined time interval after the transmitter pulse. This delay can be calibrated by reference to the calibration rings on the PPI. Unit No.74A may be switched in or out of the circuit, as desired.

in (1 - A) where A - amplification factor of V2. When the

#### DETAILED TECHNICAL DESCRIPTION

# ACTION OF DELAY CHASSIS SWITCH (see Figs. 1 and 2)

- Position (1) The input trigger is bypassed through the delay NORMAL chassis to give normal instantaneous sweep triggering with the B+ for the blocking "oscillator" switched off.

- Position (2) The input trigger from the modulator is delayed by using it to trigger a phantastron. The trailing edge of its output triggers a blocking pulse generator whose output pulse starts the sweep on the PPI.

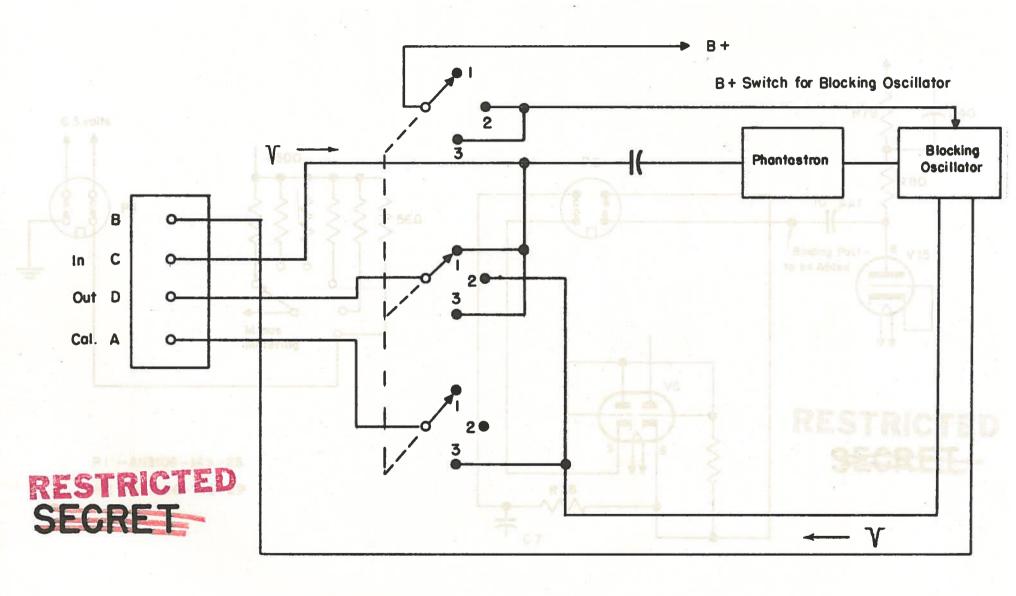

- Position (3) Both the delay chassis and the sweeps are triggered together by the modulator pulse. The delayed pulse so derived is coupled into the video via the plate of V<sub>15</sub> in chassis No.74.

The new "range ring" produced can be brought into coincidence with any 10,000 yard range ring so that on DELAY, the range indicated has this present range added to give the actual range of a target.

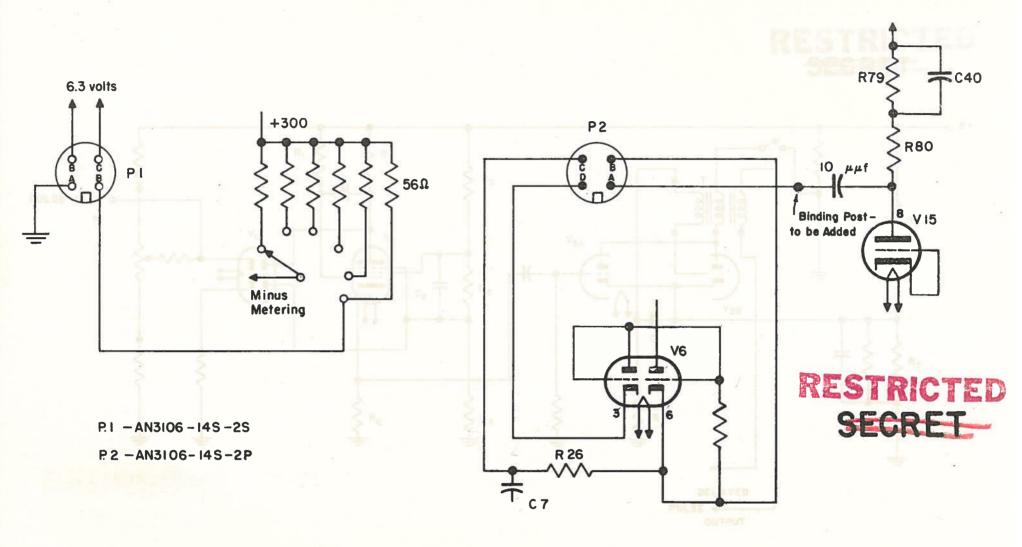

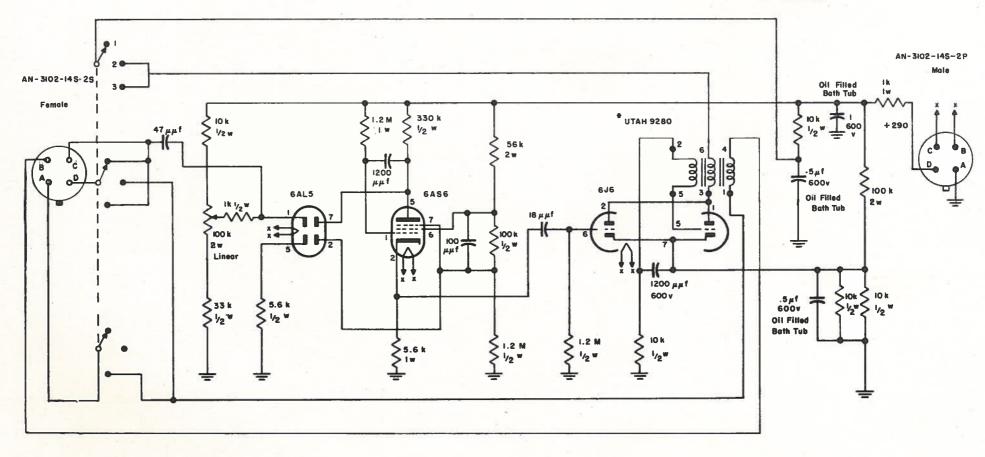

#### CIRCUIT ACTION (see Figs. 3 and 4)

### Phantastron V<sub>1A</sub>, V<sub>1B</sub>, V<sub>2</sub>

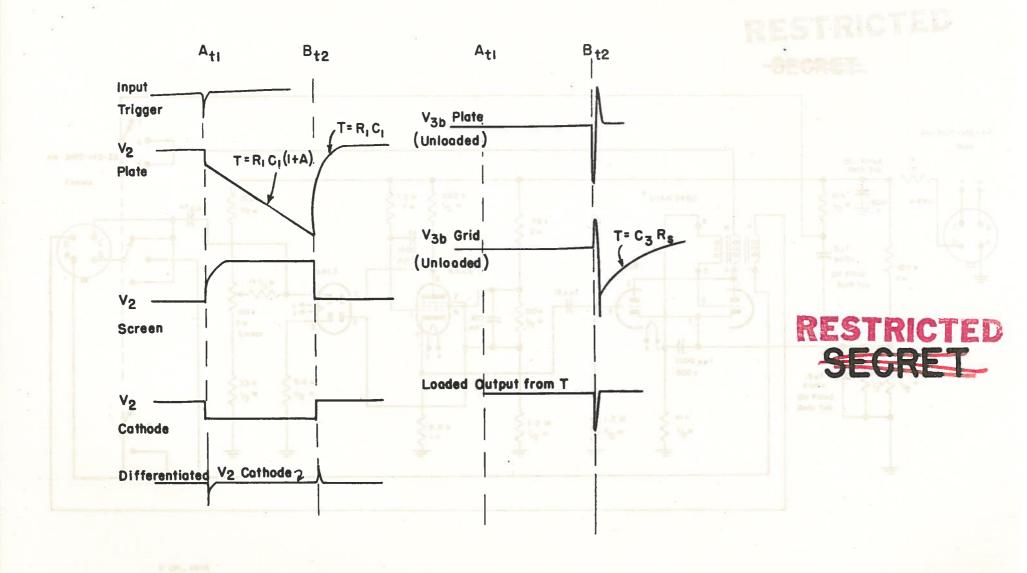

In the quiescent state, the screen of Vo is conducting heavily and no current flows in the plate circuit by virtue of suppressor cut-off. On application of a negative trigger via diode V1A to the plate of V2, the plate drops, and, with it, grid No.1 drops by coupling through C1, reducing the current to the screen. The sudden reduction in screen current in the resistor Ro causes the suppressor to rise via Ro, Ro, and speedup condenser C2. This action allows the plate to conduct. Note that the plate and grid of V2 are coupled by C1, R1, so that the plate-fall rate is limited by the discharge of C1 through R1 and by the rate of change of potential between the grid and plate. Thus the plate falls with an effective time constant  $R_1$   $C_1$  (1 + A) where A = amplification factor of  $V_2$ . When the plate bottoms, the screen current increases causing the screen voltage to fall. This fall is coupled to the suppressor, cutting off plate current, and the plate rises through time constant  $c_1 \ R_{L^{\circ}}$  Diode  $v_{1A}$  is used to terminate the plate rise, and hence to give delay control.

Since the cathode resistor, R<sub>c</sub>, of V<sub>2</sub> conducts plate current, then screen current, a change from low plate current to high screen current causes a sharp rise in cathode voltage and vice versa.

The rising edge of the cathode rectangular wave is differentiated and used to trigger the blocking pulse generator.

#### Blocking Pulse Generator V3A, V3B

The cathodes and plates of  $V_{3A}$  and  $V_{3B}$  are coupled together, the cathode voltage being such that both tubes are cut off. The application of a positive trigger to the grid of  $V_{3A}$  causes the plates of  $V_{3A}$  and  $V_{3B}$  to fall. The grid and plate windings of transformer, T, are connected antiphase so that the plate fall in  $V_{3B}$  causes a sharp grid rise. The positive feedback causes  $V_{3B}$  to conduct heavily, and to discharge  $C_3$ . This action causes a sharp negative going pulse to be generated on the plate of  $V_{3B}$ . When the plate fall ceases, the plate rises sharply causing the grid voltage to go rapidly negative. (With no output loading, the plate voltage will overshoot.) Since  $C_3$  has been discharged,

the pulse generator cannot be retriggered until C3 is charged—through  $R_s$  ( $R_s$  =  $R_5$  +  $R_6$ ). The termination of the output coil of T by  $R_{26}$  in chassis No.74 eliminates the positive overshoot in the output pulse.

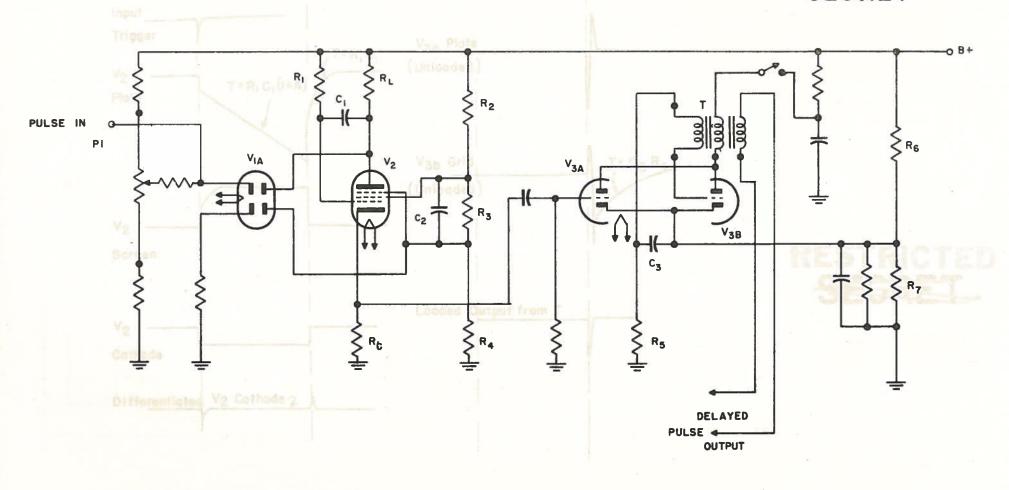

#### Waveforms

See Fig.4.

# Bringing the Equipment into Action (see Fig.5)

Set Switch 1, Unit 74A, to "calibrate". An extra ring should appear on the PPI tube. This ring can be moved in and out in range by turning potentiometer  $P_1$ , Unit 74A.

Set the delay ring to coincide with the range ring corresponding to the desired delay.

#### Operating the Delay Unit

To operate Unit 74A, set switch to "delay" and add the delay to the range read on the tube.

-000-

Fig. I SWITCHING SCHEMATIC

Fig. 2 CONNECTIONS TO UNIT 74

### RESTRICTED SEGRET

Fig. 3 SIMPLIFIED SCHEMATIC OF SWEEP DELAY CIRCUIT

Fig. 4 WAVEFORMS - SWEEP DELAY CIRCUIT

### RESTRICTED

### SECRET

# OR\_2936 9350 9340

Fig. 5 A. A. No. 4 MK. 6/I - SWEEP DELAY CIRCUIT UNIT 74A