# NRC Publications Archive Archives des publications du CNRC

### Good 150oC Retention and Fast Erase Characteristics in Charge-Trap-Engineered Memory having a Scaled Si3N4 Layer

Lina, S. H.; Chin, Albert; Yeha, F. S.; McAlister, S. P.

This publication could be one of several versions: author's original, accepted manuscript or the publisher's version. / La version de cette publication peut être l'une des suivantes : la version prépublication de l'auteur, la version acceptée du manuscrit ou la version de l'éditeur.

For the publisher's version, please access the DOI link below./ Pour consulter la version de l'éditeur, utilisez le lien DOI ci-dessous.

#### Publisher's version / Version de l'éditeur:

https://doi.org/10.1109/IEDM.2008.4796829

Electron Devices Meeting, 2008. IEDM 2008. IEEE International, pp. 1-4, 2008

#### NRC Publications Record / Notice d'Archives des publications de CNRC:

https://nrc-publications.canada.ca/eng/view/object/?id=7e66e906-0f04-40f3-92fc-04c3d1b5522dhttps://publications-cnrc.canada.ca/fra/voir/objet/?id=7e66e906-0f04-40f3-92fc-04c3d1b5522dhttps://publications-cnrc.canada.ca/fra/voir/objet/?id=7e66e906-0f04-40f3-92fc-04c3d1b5522dhttps://publications-cnrc.canada.ca/fra/voir/objet/?id=7e66e906-0f04-40f3-92fc-04c3d1b5522dhttps://publications-cnrc.canada.ca/fra/voir/objet/?id=7e66e906-0f04-40f3-92fc-04c3d1b5522dhttps://publications-cnrc.canada.ca/fra/voir/objet/?id=7e66e906-0f04-40f3-92fc-04c3d1b5522dhttps://publications-cnrc.canada.ca/fra/voir/objet/?id=7e66e906-0f04-40f3-92fc-04c3d1b5522dhttps://publications-cnrc.canada.ca/fra/voir/objet/?id=7e66e906-0f04-40f3-92fc-04c3d1b5522dhttps://publications-cnrc.canada.ca/fra/voir/objet/?id=7e66e906-0f04-40f3-92fc-04c3d1b5522dhttps://publications-cnrc.canada.ca/fra/voir/objet/?id=7e66e906-0f04-40f3-92fc-04c3d1b5522dhttps://publications-cnrc.canada.ca/fra/voir/objet/?id=7e66e906-0f04-40f3-92fc-04c3d1b5522dhttps://publications-cnrc.canada.ca/fra/voir/objet/?id=7e66e906-0f04-40f3-92fc-04c3d1b5522dhttps://publications-cnrc.canada.ca/fra/voir/objet/?id=7e66e906-0f04-40f3-92fc-04c3d1b5522dhttps://publications-cnrc.canada.ca/fra/voir/objet/?id=7e66e906-0f04-40f3-92fc-04c3d1b5522dhttps://publications-cnrc.canada.ca/fra/voir/objet/?id=7e66e906-0f04-40f3-92fc-04c3d1b5522dhttps://publications-cnrc.canada.ca/fra/voir/objet/?id=7e66e906-0f04-40f3-92fc-04c3d1b5522dhttps://publications-cnrc.canada.ca/fra/voir/objet/?id=7e66e906-0f04-40f3-92fc-04c3d1b5522dhttps://publications-cnrc.canada.ca/fra/voir/objet/?id=7e66e906-0f04-40f3-92fc-04c3d1b5522dhttps://publications-cnrc.canada.ca/fra/voir/objet/?id=7e66e906-0f04-40f3-92fc-04c3d1b5522dhttps://publications-cnrc.canada.ca/fra/voir/objet/?id=7e66e906-0f04-40f3-92fc-04c3d1b5522dhttps://publications-cnrc.canada.ca/fra/voir/objet/?id=7e66e906-0f04-40f3-92fc-04c3d1b50-04c40fa-04c40fa-04c40fa-04c40fa-04c40fa-04c40fa-04c40fa-04c40fa-04c40fa-04c40fa-04c40fa-04c40fa-04c40fa-04c40fa-04c40fa-04c40fa-04c40fa-0

Access and use of this website and the material on it are subject to the Terms and Conditions set forth at <a href="https://nrc-publications.canada.ca/eng/copyright">https://nrc-publications.canada.ca/eng/copyright</a>

READ THESE TERMS AND CONDITIONS CAREFULLY BEFORE USING THIS WEBSITE.

L'accès à ce site Web et l'utilisation de son contenu sont assujettis aux conditions présentées dans le site <a href="https://publications-cnrc.canada.ca/fra/droits">https://publications-cnrc.canada.ca/fra/droits</a>

LISEZ CES CONDITIONS ATTENTIVEMENT AVANT D'UTILISER CE SITE WEB.

#### Questions? Contact the NRC Publications Archive team at

PublicationsArchive-ArchivesPublications@nrc-cnrc.gc.ca. If you wish to email the authors directly, please see the first page of the publication for their contact information.

Vous avez des questions? Nous pouvons vous aider. Pour communiquer directement avec un auteur, consultez la première page de la revue dans laquelle son article a été publié afin de trouver ses coordonnées. Si vous n'arrivez pas à les repérer, communiquez avec nous à PublicationsArchive-ArchivesPublications@nrc-cnrc.gc.ca.

## Good 150°C Retention and Fast Erase Characteristics in Charge-Trap-Engineered Memory having a Scaled Si₃N₄ Layer

S. H. Lin<sup>a</sup>, Albert Chin<sup>b,c</sup>, F. S. Yeh<sup>a</sup>, and S. P. McAlister<sup>d</sup>

<sup>a</sup> Dept. of Electrical Engineering, National Tsing Hua Univ., Hsinchu, Taiwan, ROC

<sup>b</sup> Dept. of Electronics Engineering,, National Chiao-Tung Univ., Hsinchu, Taiwan, ROC

<sup>c</sup> Nano-Electronics Consortium of Taiwan ROC

<sup>d</sup> National Research Council of Canada, Ottawa, Canada

Tel: +886-3-5731841; Email: albert\_achin@hotmail.com

#### **Abstract**

We report a new charge-trap-engineered flash non-volatile memory that has combined 5nm Si $_3$ N $_4$  and 0.9nm EOT HfON trapping layers, within double-barrier and double-tunnel layers. At 150°C under a 100 $\mu$ s and  $\pm 16$ V P/E, this device showed good device integrity of a 5.6V initial  $\Delta V_{th}$  window and 3.8V 10-year extrapolated retention window. These data are better than the 3.3V initial  $\Delta V_{th}$  and 1.7V 10-year data for a similar structure not having the extra HfON layer.

#### Introduction

According to the International Technology Roadmap for Semiconductors (ITRS) [1], continuous down-scaling of SONOS non-volatile memory (NVM) [1]-[12] is required by scaling down the charge-trapping layer to <6nm, to suppress short-channel effects. This is challenging since the charge trapping deteriorates when the Si<sub>3</sub>N<sub>4</sub> is made thinner - for instance, very little charge trapping was shown for a 2nm Si<sub>3</sub>N<sub>4</sub> layer used as the tunnel layer of BE-SONOS [10]. The high temperature retention also gets worse when the Si<sub>3</sub>N<sub>4</sub> is thin, due to the higher trap energy in the oxide/Si<sub>3</sub>N<sub>4</sub>/oxide, arising from quantum confinement. The retention may be improved by using a BE-SONOS structure [10], but this yields low erase speeds (10~100ms). Such a retention and erase-speed trade-off is a fundamental limitation of chargetrap-flash (CTF) NVM. We have addressed this using a deep-trapping Al(Ga)N or HfON layer in a MONOS device [5]-[8]. The retention improves with increasing electron affinity  $(E_{vac}-E_C)$ , going from Al(Ga)N to HfON. By using an Al(Ga)N trapping layer, rather than Si<sub>3</sub>N<sub>4</sub>, the retention improves in a SONOS device, as confirmed by Samsung [9]. Here we report a novel charge-trap-engineered flash (CTEF) NVM device. This combines a 5nm Si<sub>3</sub>N<sub>4</sub> with a 0.9nm EOT layer of HfON, within double-barrier and double-tunnel layers, and still shows good retention and a large memory window. At 150°C and ±16V program/erase (P/E), the device showed a P/E speed of 100 $\mu$ s, an initial  $\Delta V_{th}$  window of 5.6V and an extrapolated 10-year retention of 3.8V. These results are much better than those of a control CTF device with a single Si<sub>3</sub>N<sub>4</sub> trapping layer, which had a smaller initial  $\Delta V_{th}$ and poorer 10-year retention. The improvement in the memory window in the new device indicates the better trapping capability of the Si<sub>3</sub>N<sub>4</sub>-HfON structure, at a penalty

of only extra 0.9nm for the EOT. We attribute the improved 150°C retention in the CTEF devices to charges, trapped in shallow-energy traps in the thin Si<sub>3</sub>N<sub>4</sub> layer, relaxing into deeper energy ones in the HfON layer, rather than leaking out. The 10<sup>5</sup>-cycled window was found to be 4.9V. These results compare well with other data [2]-[12], with respect to the 150°C retention, speed and memory window.

#### **Experimental Details**

The layers of the TaN-[SiO<sub>2</sub>-LaAlO<sub>3</sub>]-[Si<sub>3</sub>N<sub>4</sub>-HfON]-[LaAlO<sub>3</sub>-SiO<sub>2</sub>]-Si CTEF devices comprised 2.5nm of thermal SiO<sub>2</sub>, 2.5nm of PVD LaAlO<sub>3</sub>, 5nm of reactive PVD HfON<sub>0.2</sub> [13]-[14] and 5nm of Si<sub>3</sub>N<sub>4</sub> by LPCVD. Then 8nm LaAlO<sub>3</sub> by PVD, 5nm SiO<sub>2</sub> by PECVD, and 200nm TaN by PVD. This was followed by standard gate definition, self-aligned P<sup>+</sup> implantation and an RTA. The LaAlO<sub>3</sub> was obtained from mixed Al<sub>2</sub>O<sub>3</sub> and La<sub>2</sub>O<sub>3</sub> dielectrics, used for  $V_t$  tuning and  $V_{fb}$  shifting [15]-[20] for 32 nm node high- $\kappa$  p- and n-MOSFETs. For comparison, control devices having a single layer of Si<sub>3</sub>N<sub>4</sub> CTF, and a similar structure, were made. The devices were measured by P/E, cycling and retention to 150°C.

#### **Results and Discussion**

#### A. P/E Characteristics:

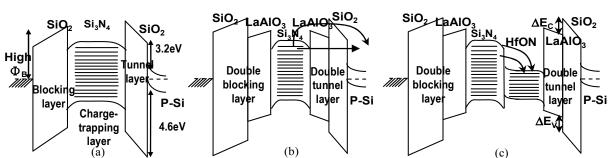

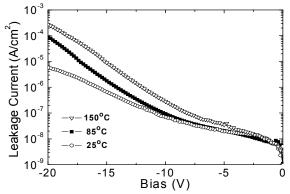

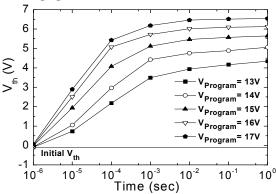

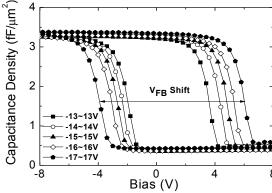

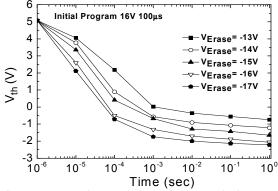

In Fig. 1 we compare, schematically, the conventional MONOS, double-barrier double-tunnel single-Si<sub>3</sub>N<sub>4</sub>-trapping CTF, and double-barrier double-tunnel double- shallow- and deep-trapping-energy-layer CTEF devices. The use of double LaAlO<sub>3</sub>-SiO<sub>2</sub> tunnel layers permits a faster P/E. This arises from the  $\Delta E_C$  and  $\Delta E_V$  in the LaAlO<sub>3</sub>/SiO<sub>2</sub> which gives better electron and hole tunneling during the program and erase procedures. The increased physical thickness, arising from the use of a high-κ layer, improves the retention. The addition of HfON in the Si<sub>3</sub>N<sub>4</sub>-HfON stack provides a deep trapping energy, for only an extra 0.9nm for the EOT. This also improves the retention through charge confinement with respect to the high- $\kappa$  LaAlO<sub>3</sub> layer. Fig. 2 displays the J-V erase characteristics indicating small leakage up to 150°C. A large C-V hysteresis of 6.6~9.9V was found under  $\pm$  13~17V sweep (Fig. 3). In Figs. 4-5 we show the  $V_{th}$  shift for the program and erase cases. A P/E time of 100µs was measured at  $\pm 16$ V, along with a large  $\Delta V_{th}$ , yielding a memory window of 5.6V in the CTEF device. For comparison, the program

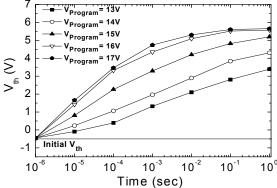

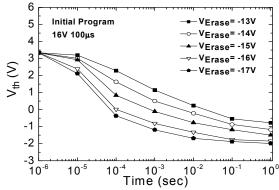

and erase characteristics of a control single-Si<sub>3</sub>N<sub>4</sub>-trapping CTF device (Figs. 6-7) show that the  $\Delta V_{th}$  is smaller and has a smaller memory window of 3.3V at  $\pm 16$ V  $100\mu$ s P/E.

#### B. Retention & Cycling:

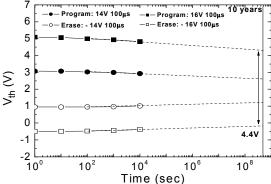

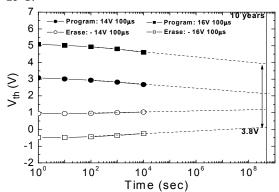

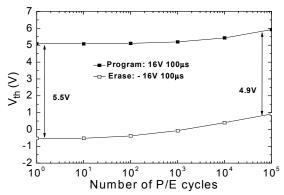

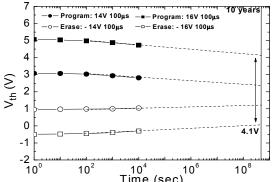

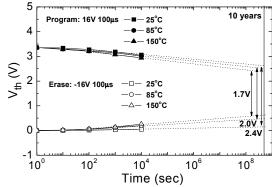

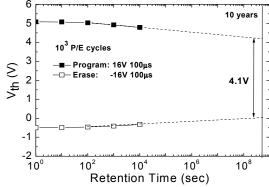

The retention data at 25, 85 and 150°C are displayed in Figs. 8-10. The extrapolated 10-year memory window decreases with increasing temperature. At 150°C, an initial  $\Delta V_{th}$  of 5.6V and 10-year window of 3.8V were measured at 100  $\mu$ s and  $\pm 16V$  P/E. The  $10^2 \sim 10^3$  times faster erase times, compared with a BE-SONOS design [10], are due to the lower hole tunneling energy barrier,  $\Delta E_V$ , between the LaAlO<sub>3</sub> and the SiO<sub>2</sub> in the CTEF devices. This design is possible due to the existing  $\Delta E_V$  and  $\Delta E_C$  between HfON trapping layer and high-κ LaAlO<sub>3</sub> tunneling layers for both fast hole tunneling erase and trapped electron retention, respectively. Meanwhile good retention is also maintained by physically thicker double LaAlO<sub>3</sub>-SiO<sub>2</sub> confinement and that stored charges relax from the shallow-trap-energy in the Si<sub>3</sub>N<sub>4</sub> into deeper traps in the HfON [13]-[14] (see Fig. 1(c)). The large 10-year window would allow 4 logic levels, as in multi-level cells (MLC), since there is an average of ~1.3V between the levels at 150°C. For comparison, the retention data of a control device appear in Fig. 11. A 3.3V initial  $\Delta V_{th}$ and 1.7V 10-year extrapolated memory window were found much worse than data for the CTEF device. The endurance was good: viz. a large 10<sup>5</sup>-cycle window of 4.9V and  $10^3$ -cycled 10-year retention window of 4.1V, at  $\pm 16$ V 100 $\mu$ s P/E (Figs. 12-13). This performance occurs because the rapid P/E produces less stress and trap-generation in the 3nm EOT LaAlO<sub>3</sub>-SiO<sub>2</sub> tunnel oxide. Table 1 compares and summarizes the memory data. Our CTEF device data compares well with that for other devices [2]-[12], and shows a larger memory window, better 150°C retention and higher speed.

#### **Conclusions**

We report a new CTEF NVM device with excellent 10-year extrapolated retention window of 3.8V from an initial 5.6V memory window at  $150^{\circ}$ C, at  $100\mu$ s and a  $\pm 16V$  P/E. This was realized by using combined shallow- and deep-trapping layers of  $Si_3N_4$ -HfON.

#### Acknowledgments

The authors at NCTU like to thank Director T. B. Wu at Materials Sci. Eng. Dept., National Tsing Hua University for the help.

#### References

- International Technology Roadmap for Semiconductors (ITRS), 2007, Process Integration, Devices, & Strucure Chapter, p. 40, 44. www.itrs.net

- [2] C. H. Lee, K. I. Choi, M. K. Cho, Y. H. Song, K. C. Park, and K. Kim, "A novel SONOS structure of SiO<sub>2</sub>/SiN/Al<sub>2</sub>O<sub>3</sub> with TaN metal gate for multi-giga bit flash memories," *IEDM Tech. Dig.*, 2003, pp. 613-616.

- [3] M. Specht, R. Kommling, L. Dreeskornfeld, W. Weber, F. Hofmann, D. Alvarez, J. Kretz, R.J. Luyken, W. Rosner, H. Reisinger, E. Landgraf, T.

- Schulz, J. Hartwich, M. Stadele, V. Klandievski, E. Hartmann, and L. Risch, "Sub-40nm tri-gate charge trapping nonvolatile memory cells for high-density applications," *Symp. on VLSI Tech. Dig.*, 2004, pp. 244-245.

- [4] C. W. Oh, S. D. Suk, Y. K. Lee, S. K. Sung, J. Choe, S. Lee, D. U. Choi, K. H. Yeo, M. S. Kim, S. Kim, M. Li, S. H. Kim, E. Yoon, D. Kim, D. Park, K. Kim, and B. Ryu, "Damascene gate FinFET SONOS memory implemented on bulk silicon wafer," *IEDM Tech. Dig.*, 2004, pp. 893-896.

- [5] C. H. Lai, Albert Chin, K. C. Chiang, W. J. Yoo, C. F. Cheng, S. P. McAlister, C. C. Chi, and P. Wu, "Novel SiO<sub>2</sub>/AlN/HfAlO/IrO<sub>2</sub> memory with fast erase, large □V<sub>th</sub> and good retention," in *Symp. on VLSI Tech. Dig.*, 2005, pp. 210-211.

- [6] Albert Chin, C. C. Laio, K. C. Chiang, D. S. Yu, W. J. Yoo, G. S. Samudra, S. P. McAlister, and C. C. Chi, "Low voltage high speed SiO<sub>2</sub>/AlGaN/AlLaO<sub>3</sub>/TaN memory with good retention," in *IEDM Tech. Dig.*, 2005, pp. 165-168.

- [7] C. H. Lai, Albert Chin, H. L. Kao, K. M. Chen, M. Hong, J. Kwo, and C. C. Chi, "Very Low voltage SiO<sub>2</sub>/HfON/HfAlO/TaN memory with fast speed and good retention," in *Symp. on VLSI Tech. Dig.*, 2006, pp. 54-55.

- [8] H. J. Yang, Albert Chin, S. H. Lin, F. S. Yeh, and S. P. McAlister, "Improved high temperature retention for charge-trapping memory by using double quantum barriers," *IEEE Electron Device Lett.*, vol. 29, pp. 386-388, April 2008.

- [9] K. H. Joo, C. R. Moon, S. N. Lee, X. Wang, J. K. Yang, I. S. Yeo, D. Lee, O. Nam, U. I. Chung, J. T. Moon, and B. I. Ryu, "Novel charge trap devices with NCBO trap layers for NVM or image sensor," in *IEDM Tech. Dig.*, 2006, pp. 979–982.

- [10] H. T. Lue, S. Y. Wang, E. K. Lai, Y. H. Shih, S. C. Lai, L. W. Yang, K. C. Chen, J. Ku, K. Y. Hsieh, R. Liu, and C. Y. Lu, "BE-SONOS: A Bandgap Engineered SONOS with Excellent Performance and Reliability", in *IEDM Tech. Dig.*, 2005, pp. 547-550.

- [11] T. Sugizaki, M. Kobayashi, M. Ishidao, H. Minakata, M. Yamaguchi, Y. Tamura, Y. Sugiyama, T. Nakanishi, and H. Tanaka, "Novel multi-bit SONOS type flash memory using a high-k charge trapping layer," Symp. on VLSI Tech., 2003, pp. 27-28.

- [12] M. Fukuda, T. Nakanishi, and Y. Nara, "Scaled 2bit/cell SONOS type nonvolatile memory technology for sub-90nm embedded application using SiN sidewall trapping structure," *IEDM Tech. Dig.*, 2003, pp. 000-012

- [13] H. J. Yang, Albert Chin, W. J. Chen, C. F. Cheng, W. L. Huang, I. J. Hsieh, and S. P. McAlister, "A program-erasable high-κ Hf<sub>0.3</sub>N<sub>0.2</sub>O<sub>0.5</sub> MIS capacitor with good retention," *IEEE Electron Device Lett.*, vol. 28, pp. 913-915, Oct. 2007.

- [14] H. J. Yang, C. F. Cheng, W. B. Chen, S. H. Lin, F. S. Yeh, S. P. McAlister, and Albert Chin, "Comparison of MONOS memory device integrity when using Hf<sub>1-x-y</sub>N<sub>x</sub>O<sub>y</sub> trapping layers with different N compositions," *IEEE Trans. Electron Device*, vol. 55, pp. 1417-1423, June 2008.

- [15] A. Chin, C. C. Liao, C. H. Lu, W. J. Chen, and C. Tsai, "Device and Reliability of High-k Al<sub>2</sub>O<sub>3</sub> Gate Dielectric with Good Mobility and Low D<sub>it</sub>," Symp. on VLSI Tech. Dig., 1999, pp. 133-134.

- [16] A. Chin, Y. H. Wu, S. B. Chen, C. C. Liao, and W. J. Chen, "High quality La<sub>2</sub>O<sub>3</sub> and Al<sub>2</sub>O<sub>3</sub> gate dielectrics with equivalent oxide thickness 5-10Å," *Symp. on VLSI Tech. Dig.*, 2000, pp. 16-17.

- [17] Y. H. Wu, M. Y. Yang, A. Chin, and W. J. Chen, "Electrical characteristics of high quality La<sub>2</sub>O<sub>3</sub> dielectric with equivalent oxide thickness of 5Å," *IEEE Electron Device Lett.* 21, 341, 2000.

- [18] C. H. Wu, B. F. Hung, Albert Chin, S. J. Wang, X. P. Wang, M.-F. Li, C. Zhu, Y. Jin, H. J. Tao, S. C. Chen, and M. S. Liang "High temperature stable [Ir<sub>3</sub>Si-TaN]/HfLaON CMOS with large work-function difference," *IEDM Tech. Dig.*, 2006, pp. 617-620.

- [19] C. F. Cheng, C. H. Wu, N. C. Su, S. J. Wang, S. P. McAlister and Albert Chin, "Very low V<sub>t</sub> [Ir-Hf]/HfLaO CMOS using novel self-aligned low temperature shallow junctions," *IEDM Tech. Dig.*, 2007, pp. 333-336.

- [20] C. C. Liao, Albert Chin, N. C. Su, M.-F. Li, and S. J. Wang, "Low V<sub>t</sub> gate-first Al/TaN/[Ir<sub>3</sub>Si-HfSi<sub>2-x</sub>]/HfLaON CMOS using simple process," Symp. on VLSI Tech. Dig., 2008, pp. 190-191.

Fig. 1. Schematic energy band diagram of (a) conventional MONOS, (b) double-barrier, double-tunnel and single-Si<sub>3</sub>N<sub>4</sub> charge-trapping flash (CTF) memory (control), and (c) charge-trapping-engineered flash (CTEF) non-volatile memory with shallow- and deep- trapping layers and additional  $\Delta E_C$  in trapping layer to double-tunnel layers (this work).

Fig. 2.  $J_g$ - $V_g$  curves for CTEF devices.

Fig. 4. Program characteristics of CTEF devices for different voltages & times.

Fig. 6. Program characteristics of a single-Si<sub>3</sub>N<sub>4</sub>-trapping, double-barrier and double-tunnel CTF device for different voltages & times.

Fig. 3. C-V hysteresis of CTEF devices.

Fig. 5. Erase characteristics of CTEF devices at different voltages & times.

Fig. 7. Erase characteristics of a single-Si<sub>3</sub>N<sub>4</sub>-trapping, double-barrier and double-tunnel CTF device for different voltages & times.

Fig. 8. Retention characteristics of CTEF devices at 25°C.

Fig. 10. Retention characteristics of CTEF devices at 150°C.

Fig. 12. Endurance characteristics of CTEF devices.

Fig. 9. Retention characteristics of CTEF devices at  $85^{\circ}\text{C}$ .

Fig.11. Retention characteristics of single-Si<sub>3</sub>N<sub>4</sub>-trapping, double-barrier and double-tunnel CTF devices at 25°C, 85°C and 150°C.

Fig. 13. 1K cycled retention data of CTEF devices.

|                                                                                                 | P/E conditions for retention & cycling | Initial $\Delta V_{th}(V)$ | △V <sub>th</sub> (V) for 10-year retention @ 85°C | $\Delta V_{th}$ (V) for 10-year retention @ 150°C | △V <sub>th</sub> (V)<br>@Cycles |

|-------------------------------------------------------------------------------------------------|----------------------------------------|----------------------------|---------------------------------------------------|---------------------------------------------------|---------------------------------|

| This Work (CTEF)                                                                                | 16V 100μs/-16V 100μs                   | 5.6                        | 4.1                                               | 3.8                                               | 4.9@10 <sup>5</sup>             |

| This Work (single-trapping Si <sub>3</sub> N <sub>4</sub> CTF)                                  | <b>16V 100</b> μs/- <b>16V 100</b> μs  | 3.3                        | 2.0                                               | 1.7                                               | •                               |

| TANOS SiO <sub>2</sub> /Si <sub>3</sub> N <sub>4</sub> /Al <sub>2</sub> O <sub>3</sub> /TaN [2] | 13.5V 100μs/-13V 10ms                  | 4.4                        | 2.07                                              | -                                                 | 4@10 <sup>5</sup>               |

| Tri-gate SiO <sub>2</sub> /Si <sub>3</sub> N <sub>4</sub> /SiO <sub>2</sub> [3]                 | 11.5V 3ms/-11.5V 100ms                 | 1.2                        | 1.1 (@25°C)                                       | -                                                 | 1.5@10⁴                         |

| FinFET SiO <sub>2</sub> /Si <sub>3</sub> N <sub>4</sub> /SiO <sub>2</sub> [4]                   | 13V 10μs/-12V 1ms                      | 4.5                        | 2.4                                               | -                                                 | 3.5@10 <sup>4</sup>             |

| SiO <sub>2</sub> /AIN/AIHfO/IrO <sub>2</sub> [5]                                                | 13V 100μs/-13V 100μs                   | 3.7                        | 1.9                                               | -                                                 | 2.9 @ 10 <sup>5</sup>           |

| SiO <sub>2</sub> /AlGaN/AlLaO <sub>3</sub> [6]                                                  | 11V100μs/-11V 100μs                    | 3.0                        | 1.6                                               | -                                                 | 2.3@10 <sup>5</sup>             |

| SiO <sub>2</sub> /HfON/AIHfO/TaN [7]                                                            | 8V 100μs/-8V 100μs                     | 2.5                        | 1.45                                              | -                                                 | 2.1@10 <sup>5</sup>             |

Table 1. Comparisons of P/E voltage, speed, initial  $\Delta V_{th}$ , extrapolated for 10-year retention at 85 and 150°C and endurance.