# NRC Publications Archive Archives des publications du CNRC

## **Transition of MEMS Technology to Nanofabrication**

Luesebrink, Helge; Glinsner, Thomas; Jakeway, Stephen C.; Crabtree, H. J; Cameron, Neil S.; Roberge, Helene; Veres, Teodor

This publication could be one of several versions: author's original, accepted manuscript or the publisher's version. / La version de cette publication peut être l'une des suivantes : la version prépublication de l'auteur, la version acceptée du manuscrit ou la version de l'éditeur.

For the publisher's version, please access the DOI link below./ Pour consulter la version de l'éditeur, utilisez le lien DOI ci-dessous.

#### Publisher's version / Version de l'éditeur:

https://doi.org/10.1166/jnn.2005.129

Journal of Nanoscience & Nanotechnology, 10, pp. 1-5, 2005-06-01

### NRC Publications Record / Notice d'Archives des publications de CNRC:

https://nrc-publications.canada.ca/eng/view/object/?id=32bf373e-a00d-48a7-893e-0e2c18968ca7 https://publications-cnrc.canada.ca/fra/voir/objet/?id=32bf373e-a00d-48a7-893e-0e2c18968ca7

Access and use of this website and the material on it are subject to the Terms and Conditions set forth at <a href="https://nrc-publications.canada.ca/eng/copyright">https://nrc-publications.canada.ca/eng/copyright</a>

READ THESE TERMS AND CONDITIONS CAREFULLY BEFORE USING THIS WEBSITE.

L'accès à ce site Web et l'utilisation de son contenu sont assujettis aux conditions présentées dans le site <a href="https://publications-cnrc.canada.ca/fra/droits">https://publications-cnrc.canada.ca/fra/droits</a>

LISEZ CES CONDITIONS ATTENTIVEMENT AVANT D'UTILISER CE SITE WEB.

#### Questions? Contact the NRC Publications Archive team at

PublicationsArchive-ArchivesPublications@nrc-cnrc.gc.ca. If you wish to email the authors directly, please see the first page of the publication for their contact information.

Vous avez des questions? Nous pouvons vous aider. Pour communiquer directement avec un auteur, consultez la première page de la revue dans laquelle son article a été publié afin de trouver ses coordonnées. Si vous n'arrivez pas à les repérer, communiquez avec nous à PublicationsArchive-ArchivesPublications@nrc-cnrc.gc.ca.

# Transition of MEMS Technology to Nanofabrication

Helge Luesebrink,<sup>1,\*</sup> Thomas Glinsner,<sup>1</sup> Stephen C. Jakeway,<sup>2</sup> H. John Crabtree,<sup>2</sup>

Neil S. Cameron,<sup>3</sup> Hélène Roberge,<sup>3</sup> and Teodor Veres<sup>3</sup>

<sup>1</sup>EV Group, Inc., 1210 Pontiac Avenue, Cranston, RI 02909, USA

<sup>2</sup>Micralyne, Inc., 1911-94 Street, Edmonton, AB T6N 1E6, Canada

<sup>3</sup>Industrial Materials Institute (NRC), 75 de Mortagne Boulevard, OC J4B 6Y4, Canada

The transition of MEMS technology to nano-fabrication is a solution to the growing demand for smaller and high-density feature sizes in the nanometer scale. Nanoimprint lithography (NIL) techniques for fabricating micro- and nano-features are discussed including hot embossing lithography (HEL), UV Molding (UVM) and micro contact printing ( $\mu$ CP). Recent results in micro and nano-pattern transfer are presented where features ranged from <100 nm to several centimeters. We also present a comparative study between standard glass microfluidic chips and their HEL counterparts by metrology. Hot-embossed microfluidic chips are shown to be faithful replicates of their parent stamps. NIL is presented as a promising avenue for low-cost, high throughput micro and nano-device fabrication.

#### Keywords:

#### 1. INTRODUCTION

The commercialization of MEMS technology has been successfully developed over the past 25 years since MEMS R&D projects were established worldwide. Many of these projects led to commercialized products including pressure sensors, inkjet printer heads, gyros and sensors for various types of applications. Some of the key contributors for MEMS successes have been the drive for infrastructure, roadmaps, industry associations, standardization of processes and sequences as well as their automation, which resulted in turn-key solutions for low cost, high yield, and high volume wafer level processing.

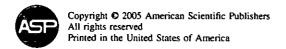

Currently, nanotechnology exists primarily in R&D laboratories, but transfer of MEMS R&D and production technology will continue to accelerate the development of commercial nanofabrication methods. Furthermore, the increasing demand for polymer-based devices coupled with low-cost fabrication technologies underscores the need to develop direct-process protocols where flow channels, reservoirs, mixing chambers and other device components are manufactured directly in a polymer chip. Nanoimprint Lithography (NIL) techniques including hot embossing (HEL)<sup>2</sup> and UV-molding (UVM) are among the most used methods of structuring of polymers. NIL is a patterning method in which a material is deformed with a re-usable and pre-patterned stamp. Structures are transferred into heat-softened resists with the HEL process and are cured by cooling the polymer below its glass transition temperature  $(T_g)$ . Similarly, in UVM, the structures are created as for HEL, but are then cured by UV photopolymerization. A related process called micro-contact printing  $(\mu CP)$  often refers to the transfer of 'inked' materials on a patterned surface, typically to a metallic or metallized substrate.<sup>3</sup>

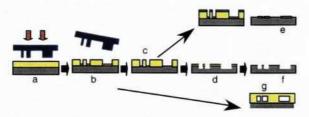

An overview of these methods is presented in Figure 1. Even though most nanotechnology devices are still being developed within R&D initiatives, among the many future areas of application are: drug delivery systems and analysis systems (BioMEMS, microfluidics), genomics, proteomics, optics, photonics, magnetic, chemical and biosensors, RF components and electronics.<sup>4-6</sup>

Indeed, imprint lithography even offers potentially significant processing short-cuts to the well-established micro and nano-fabrication industry where comparatively expensive lithographic techniques (photo, e-beam, focused

<sup>\*</sup>Author to whom correspondence should be addressed.

Fig. 1. NIL Technologies.

ion-beam) may be employed just once to create a viable stamp and the stamp can spawn hundreds of copies.<sup>7</sup>

#### 2. NIL OVERVIEW

In the following paragraphs, an overview of NIL methods (HEL, UVM,  $\mu$ CP) is presented with emphasis on process and equipment related issues. Reviews of these technologies appear regularly.<sup>8</sup>

#### 2.1. Hot Embossing

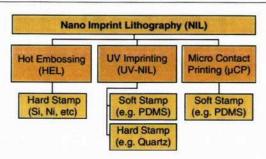

Many HEL process requirements are similar to MEMS wafer bonding technology. The main process parameters inherent to a variety of commercially available wafer bonding processes are: (i) control and uniformity of temperature and pressure over the substrate area; and (ii) atmosphere control in the bond chamber (pressure, gas etc). Figure 2 provides a breakdown of today's successful MEMS bonding processes for automotive applications, such as gyros and pressure sensors.<sup>9</sup>

In addition, HEL technology requires active cooling and temperature ramp control due to the nature of the thermoplastic substrates. This technology transfer has enabled HEL mix-and-match structures from wafer dimensions down to sub-100 nm feature size at the wafer level.

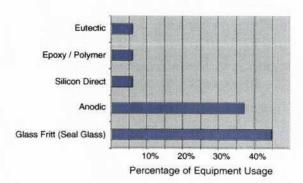

In a hot embossing process, the polymer is heated above its  $T_g$  and high contact forces are applied. A polymer (traditionally, poly(methyl methacrylate), PMMA) is

Fig. 2. Bonding processes used in today's automotive MEMS.

Fig. 3. Hot embossing process chart.

imprinted with a patterned stamp. The stamp is usually fabricated from silicon or nickel for high aspect ratio structures though other materials such as SU-8<sup>10</sup> have been employed successfully. Both the stamp and the substrate are heated to temperatures above the  $T_{\rm g}$  of the spinon-polymer thereby decreasing the polymer viscosity for the imprinting process. Application of high contact force between stamp and polymer enables cavity-filling of the stamp. After the imprinting step, the whole stack is cooled well below  $T_{\rm g}$  to cure the patterned features. The controlled separation of stamp and polymer is carried out at elevated temperatures (but below  $T_{\rm g}$ , see Fig. 3).

The equipment used in this study allows for parallel as well as for wedged de-embossing depending on the patterned feature sizes. The EVG®520 HE instrument is equipped with a high contact force hydraulic system, active cooling, and an automated de-embossing unit for imprinting of substrates of up to 200 mm in diameter.

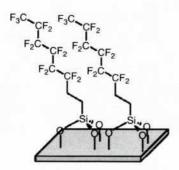

The smaller the features and the higher the density of imprinted patterns, the higher is the adhesion force between stamp and polymer. Application of an anti-stiction or release layer (often by silanization, see Fig. 4 below) and a wedged separation are the preferred methods of separating stamp and polymer.

Substrates of up to 200 mm in diameter have been successfully replicated with silicon masters. <sup>11</sup> Mixed features down to less than 100 nm (posts) were generated in preliminary tests. <sup>12</sup> Once the pattern has been transferred into the resist, standard micro-fabrication techniques

Fig. 4. Fluorosilanized silicon oxide surface.

Fig. 5. Process-flow for hot embossing lithography.

are employed to etch into the substrate. The entire process is shown schematically in Figure 5((a) imprint; (b) de-embossing; (c) de-scum, (d) etch (RIE, ICP); (e) deposition and release, (f) template or device, (g) bonding).

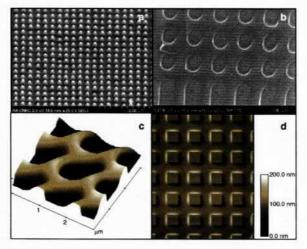

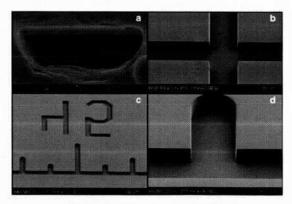

Preliminary results with resolution test stamps have been recently reported 12.13 and a selection of the most promising embossed structures (posts, holes, lines and trenches from 100 nm to several microns) is shown below in Figure 6.

The images in Figure 6 illustrate clearly the resolution advantage of 'negative' stamps where the structures are formed as the thermoplastic polymer resist flows into the stamp features (6a, 6b, 6d) rather than positive stamps where the resist is simply displaced by the stamp (6c).

#### 2.2. UV-Molding

The advantages of using mature patterning methods like reduction EUV-Lithography to create nanometer scale features on a commercial scale are often outweighed by equipment costs. Traditional methods like Electron Beam Lithography (EBL) are suitable for generating patterns in the nm-regime but are serial and therefore laboriously slow. UVM is a stamping technique, which enables processes for the development of nanotechnology devices due

**Fig. 6.** Embossed Structures: (a) FEG-SEM (Hitachi S4700) of 100 nm posts in Poly(cyclic olefin), (PCO); (b) FEG-SEM of sub micron lines and posts in PMMA; (c) AFM (Vecco NanoScope 3) of sub-micron holes; and (d), AFM of 4 μm posts in PMMA.

to its high level of resolution in the nm-range at low cost. The UVM process is performed in a modified mask aligner, which has been used for UV-lithography in semi-conductor and MEMS fabrication processes. The strengths of this instrument include the wedge compensation unit used to ensure parallelism between mask and substrate.

The main differences between HEL and UVM are: (i) transparent stamps for alignment and UV-curing of monomers are required for UVM and optional for HEL; (ii) unlike HEL, UVM processes are performed at room temperature without any heating cycles; (iii) low contact forces are applied for UVM as compared with HEL; (iv) optical alignment is standard for UVM whereas aligned HEL usually requires additional equipment such as the EVG $^{\oplus}$ 620 aligner; and (v) monomers are cross linked via UV-curing in a UVM process while thermoplastic polymers are cooled below  $T_g$  in order to harden the structures after the HEL imprinting process.

The alignment of transparent stamps to the substrate as well as the imprinting and curing process are performed in a modified aligning system of type EVG®620 for substrates up to 150 mm in diameter.

In most cases, either quartz glass stamps (hard stamps) or PDMS stamps (soft stamps) are used for UV-molding processes. The process flow of a UV-molding process is as follows: a monomer coated carrier substrate (e.g. silicon wafer) as well as the transparent stamp are loaded into the aligner and fixed by vacuum on their respective chucks. After optical alignment of substrate and the stamp is defined, they are brought into contact. The alignment accuracy of state-of-the-art mask aligners used for fabrication of MEMS devices is less than 1 µm, however the forecast accuracy for such systems is less than 100 nm in order to meet the demands for nanofabrication. An adjustable uniform contact force of up to 750 N is applied to imprint the monomer with the stamp pattern. Furthermore, an adjustable vacuum contact is applied which ensures intimate contact between stamp and substrate. The curing process of the imprinted structures is accomplished by UV-exposure with broadband wavelength from 350 nm to 450 nm.

#### 2.3. Micro Contact Printing (µ-CP)

In a  $\mu$ CP process, molecules such as thiols are transferred from an "inked stamp" to another surface (in case of thiols, gold and silver are typical). PDMS stamps are inked by placing a thin film via a droplet on the stamp surface or by applying the substances in an inked pad before the patterning process.<sup>3,14</sup>

This technology is being employed in biotechnology for surface preparation of diagnostic devices, <sup>15,16</sup> and application of adhesive patterns for UV-adhesive bonding (see Fig. 7).

Step 1: Apply Adhesive to Pad

Step 2: Transfer Adhesive to Glass Wafer

Step 3: Align and Bond to CMOS Wafer

Fig. 7. UV adhesive bonding.

#### 3. APPLICATION

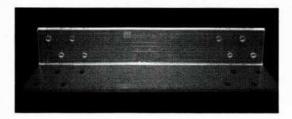

Currently, most devices in innovative micro and nano technology are related to microfluidic applications that manipulate molecules in drug discovery, delivery and diagnostics. This paper describes the comparison between a conventionally bulk-micromachined microfluidic chip (for example, see Fig. 8), an off-the-shelf chip for capillary electrophoresis from Micralyne, Inc., and a device manufactured by hot embossing.

Surface profilometry and scanning electron microscopy (SEM) were used to examine and compare the surfaces of the Si stamp master, the unbonded polymer substrate embossed with the master, and an unbonded glass analogue. Figure 9 provides a schematic of Micralyne's standard chip. Both depth and width measurements were taken at the indicated points.

Glass chip width measurements were recorded using a McBain ZIII Column (McBain Instruments, Chatsworth, California), and both polymer and silicon master measurements were recorded using a Stylus Profiler (Dektak-8, Veeco Inc., Tucson, Arizona) and confirmed by FEG-SEM (Hitachi S4700, Japan) and are shown in Table I. Five measurements were recorded at each position for the glass device while two measurements were recorded for each position on the silicon master and polymer chip.

Depth measurements were recorded using a profiler (Glass Chip: Tencor Alpha-step 200 Stylus Profiler, KLA-Tencor, San Jose, California; Silicon Master and Polymer Chip, Dektak 8 Stylus Profiler, Veeco Inc. Tucson, Arizona) and are shown in Table II. Five measurements

Fig. 8. Standard microfluidic chips (Micralyne, Inc.)

Fig. 9. Schematic of Micralyne's Standard Microfluidic Chip showing the points where width and depth measurements were taken.

**Table I.** Average width measurements with standard deviation(s) in microns at various points of Micralyne's Standard Chip (n = 5 for each position, see Fig. 9), silicon master (n = 2) and polymer chip (n = 2).

| Position       | 1 (μm)          | 2 (µm)          | 3 (µm)          |

|----------------|-----------------|-----------------|-----------------|

| Glass chip     | 53.9 ± 0.09     | 56.0 ± 0.04     | 56.4±0.25       |

| Silicon master | $48.8 \pm 0.23$ | $48.5 \pm 0.08$ | $48.7 \pm 0.15$ |

| Polymer chip   | $49.2 \pm 0.5$  | $49.4 \pm 0.2$  | $48.9 \pm 0.5$  |

**Table 11.** Depth measurements with standard deviation(s) in microns at various points of Micralyne's Standard Chip (n = 5) for each position (glass, silicon, polymer), see Fig. 9). With the silicon master, the height of the channel-forming ridge is measured.

| Position       | 1 (μm)            | 2 (µm)             | 3 (µm)            |

|----------------|-------------------|--------------------|-------------------|

| Glass chip     | 19.70 ± 0.004     | 19.70 ± 0.010      | 19.70 ± 0.005     |

| Silicon master | $22.03 \pm 0.002$ | $21.04 \pm 0.0004$ | $22.56 \pm 0.001$ |

| Polymer chip   | $22.09 \pm 0.014$ | $21.09 \pm 0.038$  | $22.68 \pm 0.007$ |

Table III. Surface roughness of the glass chip channel floor is comparable to average roughness of polymer chip channel floor.

| Surface roughness (nm) |           |  |

|------------------------|-----------|--|

| Glass chip             | 2.1 ± 0.2 |  |

| Polymer chip           | 3.5       |  |

Fig. 10. (a) SEM of Micralyne bonded glass chip cross-section (position 3 from Fig. 5). The depth of the channel is 20  $\mu$ m while the maximum width is 56  $\mu$ m. The surface roughness on the bottom of the channel is an artifact of the dicing procedure; (b) the cross-hair (position 1, Fig. 9) embossed in PCO; (c) the embossed scale-bar (position 2, Fig. 9); and (d) a close-up of the embossed scale-bar (position 2, Fig. 9).

RESEARCH ARTICLE

were recorded at each position. The glass chip was etched using a wet etch process and provides a uniform etch rate and depth. The silicon master was etched using a deep reactive ion etching procedure where the etch rate varies slightly over the surface of the wafer. This leads to the discrepancy (approximately 1.5  $\mu$ m) as shown in Table II. As the polymer chip is molded directly from the silicon master, it is expected to maintain these slight discrepancies; indeed this is what is seen with the same variation of approximately 1.5  $\mu$ m evident. Additionally, the profilometry data shows good agreement between identical positions on the silicon master and the polymer chip (e.g. position 1: silicon height is 22.03  $\mu$ m, polymer chip is 22.09  $\mu$ m). These results indicate that the polymer chip is an accurate replicate of the silicon master.

Surface roughness is an important feature for microfluidic devices where optical detection is required. A smooth surface is required to minimize reflection or refraction of light that is passed through the channel. The surface roughness each chip was measured using an atomic force microscope. The results are presented in Table III. The bottom of the channel was evaluated for surface roughness for the glass chip<sup>18</sup> and the polymer chip. The SEM results indicate that the polymer device has maintained the nanometer surface roughness that is evident in commercially available glass microfluidic devices.

Scanning electron micrographs were recorded using a LEO 435VP (LEO Electron Microscopy Ltd., Cambridge, UK and a Hitachi S4700 FEG-SEM). Figure 10a shows a cross section of a bonded Standard Chip. Figures 10b-d show embossed structures in bulk PCO with the EVG520HE and the standard Micralyne-design (Figure 9).

#### 4. CONCLUSION

The microfluidic chip surface morphology observed by profilometry and SEM of the glass and plastic substrates as well as in the silicon-master compare favorably. The integrity of the feature-transfer from master to polymer substrate is good where comparable structure dimensions were within 0.5% over tens of micrometers.

HEL is clearly a versatile tool not only for microfabricated fluidic channels, but also the techniques and expertise developed here transfers to nanofabrication where critical dimensions of many commercial devices are rapidly approaching sub 100 nm nodes. We have demonstrated HEL pattern transfer from sub-100 nm posts to channels several centimeters long.

The entire families of nanoimprinting techniques (HEL, UVM,  $\mu$ CP) are suitable methods for imprinting and transferring features in the sub-100 nm era. Much of the equipment and process experience developed in MEMS fabrication can be directly transferred to nanoimprinting techniques to produce nano-devices. Alignment systems

derived from MEMS production equipment allow for alignment accuracy in the sub- $\mu$ m range, which enables multi-level impressions. Sub-100 nm alignment accuracy systems are forthcoming for NIL tools and will play an important role in enabling low-cost, high throughput nanofabrication.

Acknowledgments: The HEL study under 2.1 was performed in part at the Cornell Nanofabrication Facility (a member of the National Nanofabrication Users Network) which is supported by the National Science Foundation under Grant ECS-9731293, its users, Cornell University and Industrial Affiliates. NSC, HR and TV are also grateful for close collaboration with Dr. Mandy Esch (CNF) as well as internal financial support and staff efforts (NRC). SCJ thanks the Natural Sciences and Engineering Research Council for Industrial Research Fellowship.

#### References and Notes

- R. H. Grace, in Commercialisation Issues of MEMS/MST/Micromachines: An updated Industry report card on the barriers to commercialisation. Proceedings of Sensors Expo, Boston (2002).

- N. Roos, T. Luxbacher, T. Glinsner, K. Pfeiffer, H. Schultz, and H.-C. Scheer, in Nanoimprint lithography with a commercial 4 inch bond system for hot embossing, Proceedings of Microlithography Conference, Santa Clara, California (2001).

- 3. Y. Xia and G. M. Whitesides, Annu. Rev. Mater. Sci. 28, 153 (1998).

- S. M. Ford, A. B. McCandless, X. Liu, and S. A. Soper, Proc. SPIE Int. Soc. Opt. Eng. 4560, 207 (2001).

- L. Montelius, B. Heidari, M. Graczyk, I. Maximov, E.-L. Sarwe, and T. G. I. Ling, Microelectronic Engineering 53, 521 (2000).

- P. Ghosh, M. L. Amirpour, W. M. Lackowski, M. V. Pishko, and R. M. Crooks, *Polymer Preprints* 40, 423 (1999).

- 7. C. Martin, L. Ressier, and J. P. Peyrade, Physica E 17, 523 (2003).

- C. R. K. Marrian and D. M. Tennant, J. Vac. Sci Technol. A 21, S207 (2003).

- 9. P. Lindner, MST News 1, 46 (2003).

- M. Esch, S. Kapur, G. Irizarry, and V. Genova, Lab Chip 3, 121 (2003).

- C. Perret, G. Gourgon, F. Lazzarino, J. Tallal, S. Landis, and R. Pelzer, in *Characterization of 8 inch wafers printed by nanoim*print lithography, Micro and Nano Engineering International Conference (2003).

- N. S. Carneron, M. C. C. Chevallier, T. Veres, S. Kapur, and M. Esch, in Hot Embossing Lithography: Interfacial Chemistry and Polymer Rheology, Montreal, QC (2003).

- N. S. Cameron, T. Veres, S. Kappur, and M. Esch, in Development of hot-embossing/nano-imprint lithography (HEL/NIL): Parameters for large-scale functional surfaces and templates, Nano Crossroads, Montreal (2002).

- B. Michel, A. Bernard, A. Bietsch, E. Delamarche, M. Geissler,

D. Junker, H. Kind, J.-P. Renault, H. Rothuizen, H. Schmid,

P. Schmidt-Winkel, R. Stutz, and H. Wolf, J. Research and Development 45 (2001).

- 15. A. Fadiel and F. Naftolin, Int. Arch. Biosci. 1111 (2003).

- 16. D. N. Gosalia and S. L. Diamond, PNAS 100, 8721 (2003).

- 17. L. Peters, Semiconductor International 19 (2003).

- B. H. Weiller, L. Ceriotti, T. Shibata, D. Rein, M. A. Roberts, J. Lichtenberg, J. B. German, N. F. de Rooij, and E. Verpoorte, Anal. Chem. 74, 1702 (2002).